Data Flow Modelling in Verilog

The VLSI IC circuits design flow is shown in the figure below. A designer aspiring to master this versatile language must first become familiar with its constructs practice their use in real applications and.

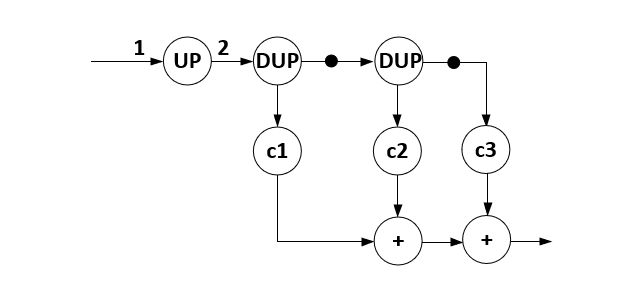

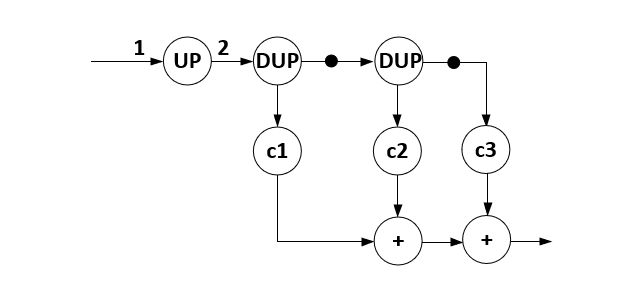

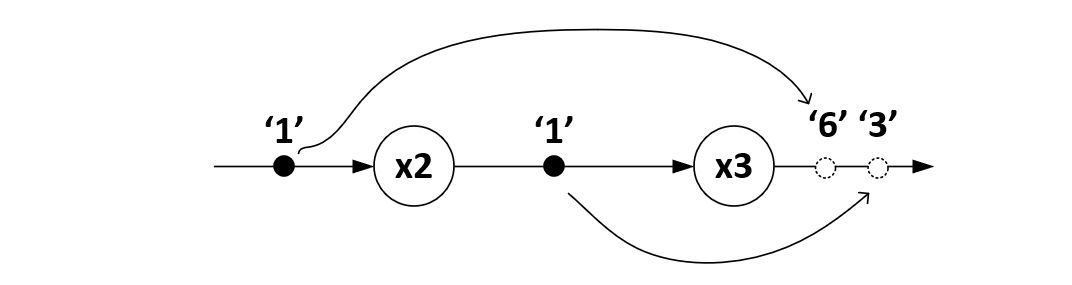

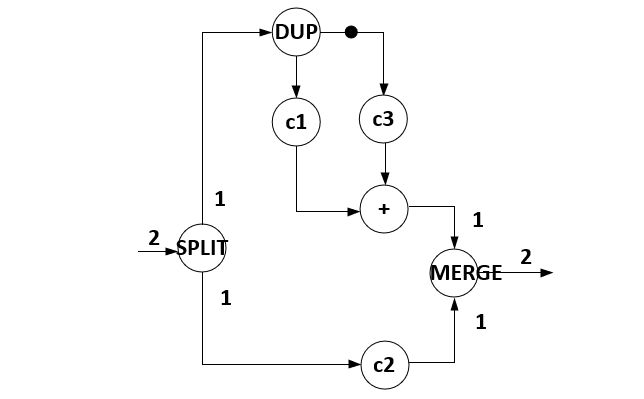

Data Flow Graph Merging Download Scientific Diagram

The various levels of design are numbered and the blocks show processes in the design flow.

. We would again start by declaring the module. Describes how the Vitis development environment lets you build a software application using the OpenCL API to run hardware kernels on accelerator cards like a Xilinx Alveo Data Center accelerator card for FPGA-based acceleration. VLSI Design Flow The VLSI IC circuits design flow is shown in the figure below.

And they are not affecting the synthesis results. Verilog code for AND gate using data-flow modeling. The various levels of design are numbered and the blocks show processes in the design flow.

Understanding the structures that underlie the programs algorithms and languages used in data science and elsewhere. A comprehensive resource on Verilog HDL for beginners and experts large and complicated digital circuits can be incorporated into hardware by using Verilog a hardware description language HDL. An example would be the data flow when a processor fetches imaging data from the system ram and executes them.

VLSI Digital System. Specifications comes first they describe abstractly the functionality interface and the architecture of the digital IC circuit to be designed. QUANT Quant internships expose you to the financial markets where youll gain experience on anything from identifying and defining significant algorithm improvements our trading strategies pricing models execution logic and.

If you are interested in algorithms performance engineering data capture and analysis trading infrastructure or exchange gateways youll love Akunacademy. Specifications comes first they describe abstractly the functionality interface and the architecture of the digital IC circuit to be designed. Using two-state variables in RTL models may enable simulators to be more efficient.

Assign Y A. The idea is that algorithms modeled in C can be converted to Verilog if the two languages have the same data types. Meanwhile the graphics engine will execute post-processed data from the previous batch dumped into another part of memory and so on.

Verilog introduces new two-state data types where each bit is 0 or 1 only. They also decide on how the data should flow inside the chip. Mastery of a particular programming language while.

Then we use assignment statements in data flow modeling. Expands computational concepts and techniques of abstraction. Endmodule Just like the and operation the logical operator performs a binary multiplication of the inputs we write.

Module AND_2_data_flow output Y input A B. Fall 2022 Development of Computer Science topics appearing in Foundations of Data Science C8.

Lecture 15 Synchronous Dataflow

No comments for "Data Flow Modelling in Verilog"

Post a Comment